План верификации

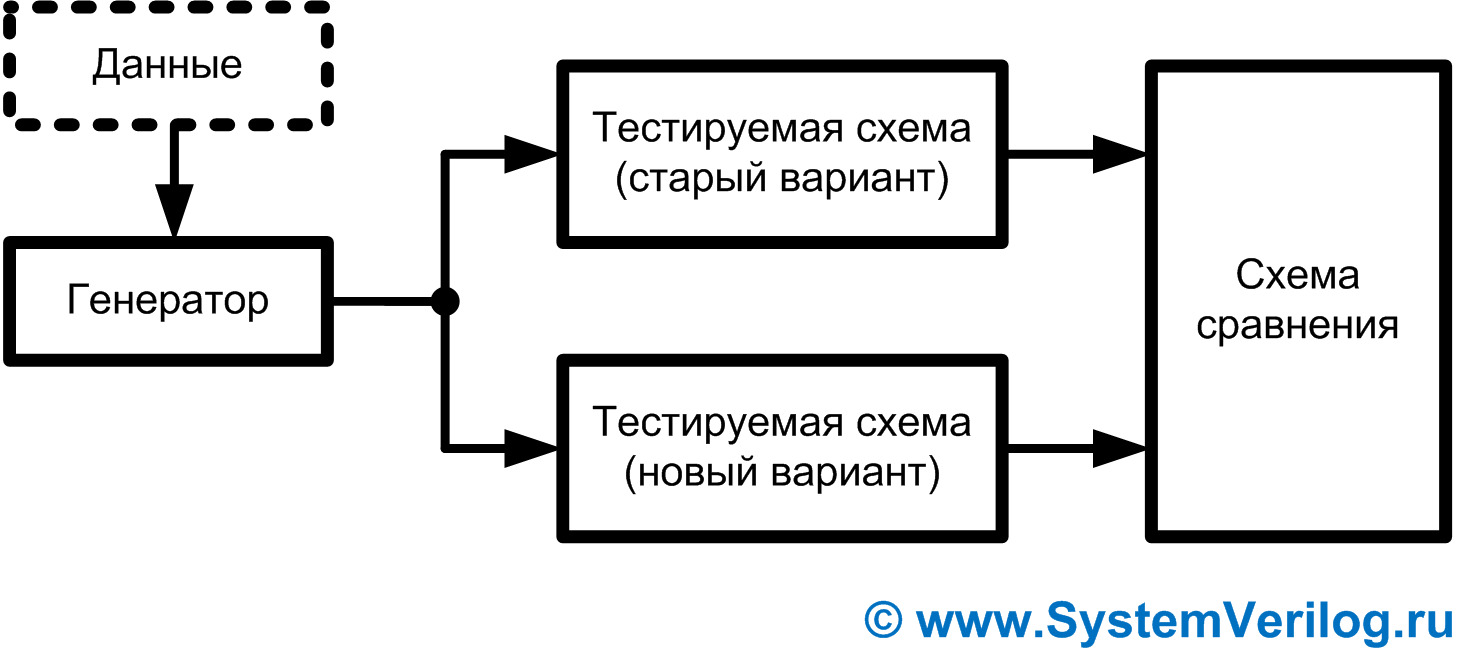

Для проверки идентичности RTL-описаний необходимо выполнить следующую последовательность действий (см. рис. 4):

1) Сгенерировать тестовые воздействия.

2) Послать эти воздействия на входы старой и новой схемы.

3) Сравнить значения на выходах схем.

Рис. 4. Схема проверки идентичности RTL-описаний

Данная цепочка действий выполняется до тех пор, пока не будет достигнут требуемый уровень функционального покрытия.

В SystemVerilog есть набор средств, позволяющих накладывать ограничения на генерацию случайных последовательностей данных. Т.е. генерировать только необходимые или разрешенные значения. Применять эти средства при проверке идентичности старого и нового варианта схемы нужно осторожно, т.к. обе схемы должны одинаково реагировать как на правильные значения, так и на неправильные.

Предполагается, что для проверки граничных значений и специальных ситуаций уже существуют написанные тесты, поэтому в работе используется подход, который предусматривает генерацию только случайных последовательностей тестовых воздействий. Такой подход значительно экономит время, т.к. позволяет максимально быстро и эффективно перебрать все входные наборы и не требует написания направленных тестов. Недостатком такого подхода является то, что может быть сгенерирована неправильная последовательность или последовательность, которая уже генерировалась. При проверке идентичности RTL-описаний об этом можно не заботиться.

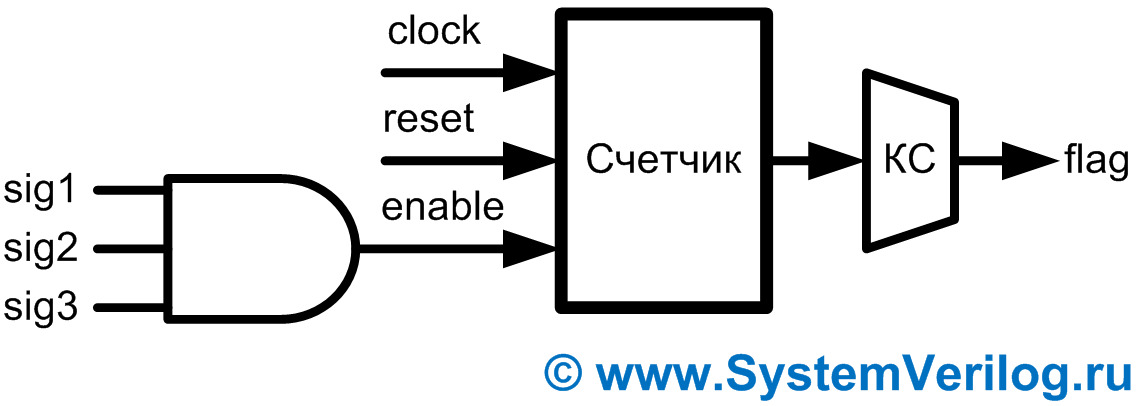

Во многих случаях генерации только случайных последовательностей тестовых воздействий будет достаточно для достижения требуемого результата. В качестве примера, когда может потребоваться направленный тест, рассмотрим схему, представленную на рис. 5. Сигнал flag установится в ‘1’ только, если сигналы sig1, sig2 и sig3 будут в ‘1’ на протяжении 8-ми тактов.

Рис. 5. Схема генерации сигнала flag

Если на генерацию сигнала не накладывать никаких ограничений, то она будет происходить по закону равномерного распределения и вероятность того, что ‘1’ будет генерироваться 8 тактов подряд, достаточно мала, а вероятность того, что сразу 3 сигнала одновременно будут в ‘1’ на протяжении 8-ми тактов еще гораздо меньше. Подобные ситуации хорошо видно на временной диаграмме. Там, где генерация случайных тестовых последовательностей не справилась, сигнал будет прибывать всегда в одном и том же состоянии.