Архитектура тестового окружения

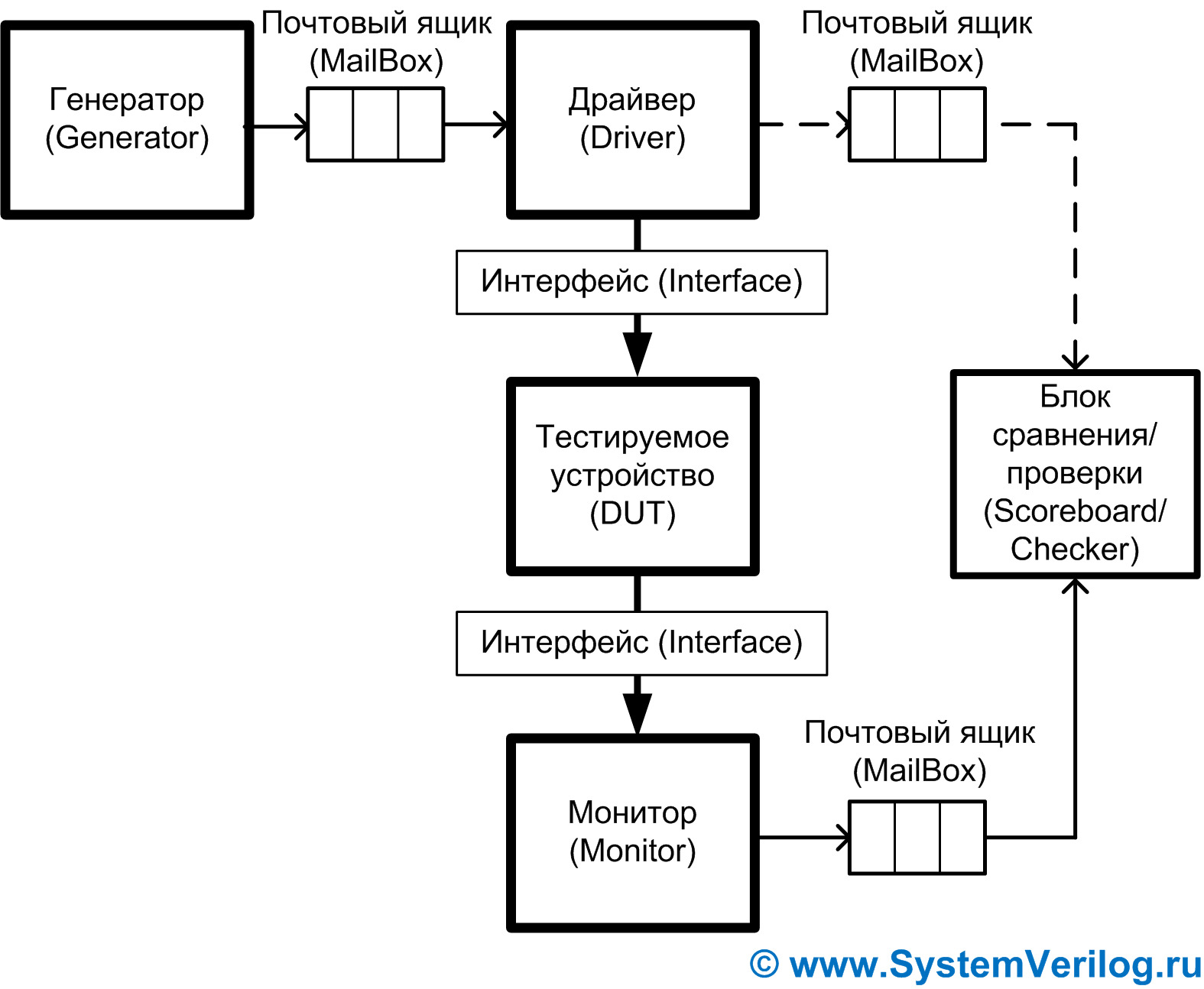

Тестовое окружение на языке SystemVerilog состоит из следующих блоков (см. рис. 6):

Рис. 6. Общая архитектура тестового окружения

- Генератор (Generator) случайных тестовых воздействий генерирует транзакции с учетом наложенных ограничений (Constraint-Random Verification – CRV) и передает их с помощью почтового ящика (MailBox) драйверу.

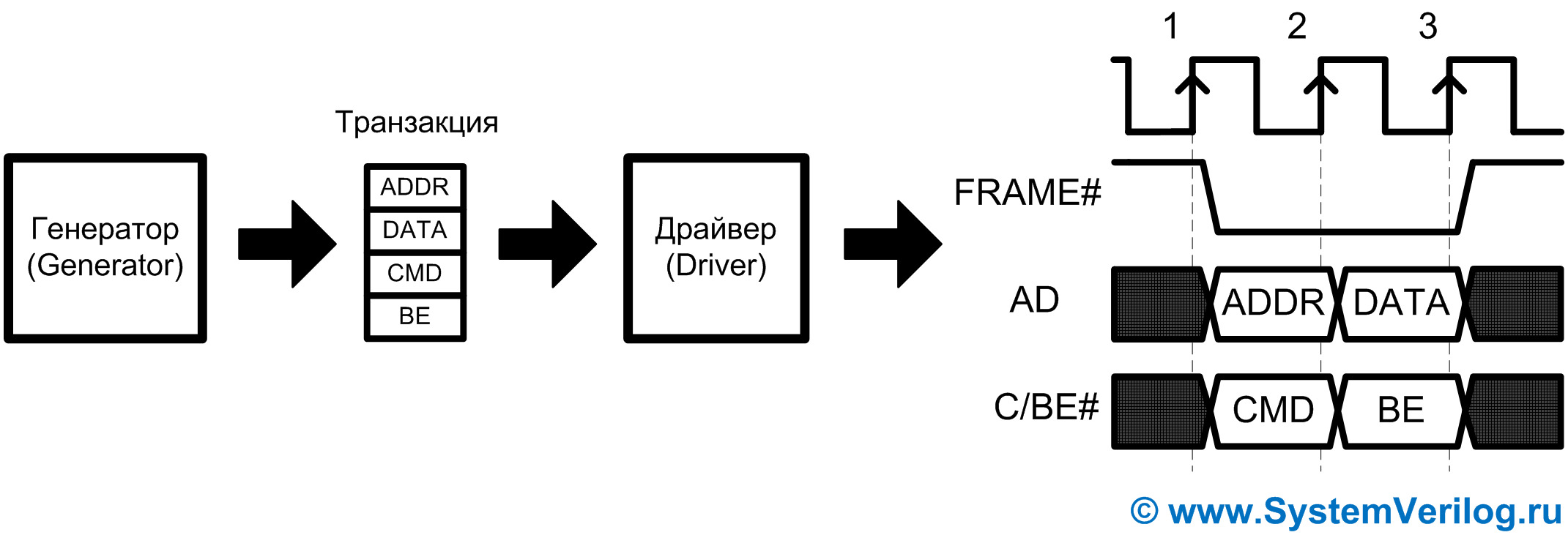

- Драйвер (Driver) по входному интерфейсу (Interface) посылает транзакцию на вход тестируемого устройства (Design Under Test — DUT). Транзакция может выдаваться за один такт или распределяться во времени в соответствии с протоколом передачи (см. рис. 7). Если взаимодействие происходит по принципу рукопожатия (Handshake), то драйверу могут понадобиться сигналы выходного интерфейса.

Рис. 7. Распределение транзакции во времени в соответствии с протоколом передачи

- Монитор (Monitor) или приемник (Receiver) принимает по выходному интерфейсу транзакцию с выходов тестируемого устройства и передает ее по почтовому ящику в блок сравнения/проверки.

- Блок сравнения (Scoreboard) или блок проверки (Checker) принимает транзакции от драйвера или монитора с помощью почтового ящика. В зависимости от задач верификации могут определенным образом сравниваться транзакции посланные драйвером и принятые монитором или же может просто проверяться правильность принятых транзакций. В случае, когда проверка выходов тестируемого устройства происходит на уровне сигналов, блок проверки может быть объединен с монитором. Широко используется блок проверки на основе SystemVerilog утверждений (SVA Checker).

- Блок оценки функционального покрытия (Coverage) собирает информацию о посланных на тестируемое устройство транзакциях. Для этого каждая посланная драйвером транзакция отправляется по почтовому ящику в блок оценки покрытия. Если драйвер передает транзакцию в блок сравнения/проверки, то можно пересылать транзакцию из него.

Можно встретить еще один блок — транзактор (Transactor или в сокращенном виде Xactor). Под этим названием подразумеваются блоки, подключенные непосредственно через интерфейс к тестируемому устройству. В нашем случае — это драйвер и монитор.

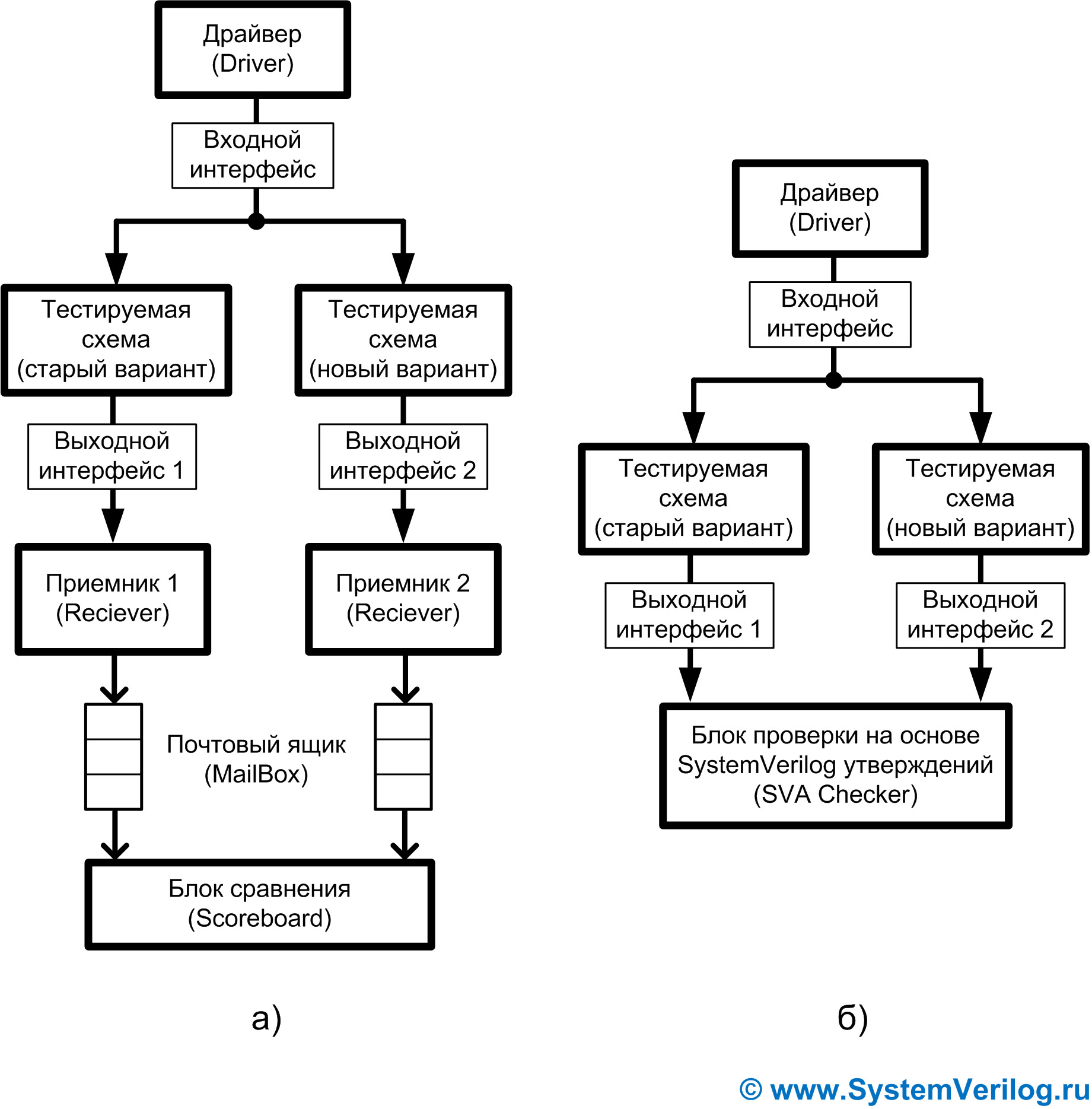

Для эффективной проверки идентичности RTL-описаний было разработано два варианта тестовых окружения (см. рис. 8). В связи с тем, что необходимо просто перебирать входные наборы, функции генератора упрощаются. Было принято решение объединить его с драйвером в один блок, благодаря чему пропадает необходимость в средствах коммуникации между этими блоками. Этот блок идентичен для обоих вариантов.

Рис. 8. Архитектура тестового окружения для проверки идентичности RTL-описаний: а) с блоком сравнения Scoreboard; б) с блоком проверки на основе SystemVerilog утверждений

Варианты тестовых окружений различаются на выходе тестируемого устройства. В первом варианте (рис. 8а) к выходам каждой тестируемой схемы с помощью интерфейса подключен приемник, который принимает транзакцию и передает ее через почтовый ящик в блок сравнения. Во втором варианте (рис. 8б) сигналы с выходов тестируемых схем напрямую через интерфейс идут в блок проверки на основе SystemVerilog утверждений (SVA Checker).

Вариант схемы тестового окружения на рис. 8а более универсален, но сложнее в реализации, чем вариант на рис. 8б. Для решения задачи проверки идентичности RTL-описаний прекрасно подходят оба варианта.